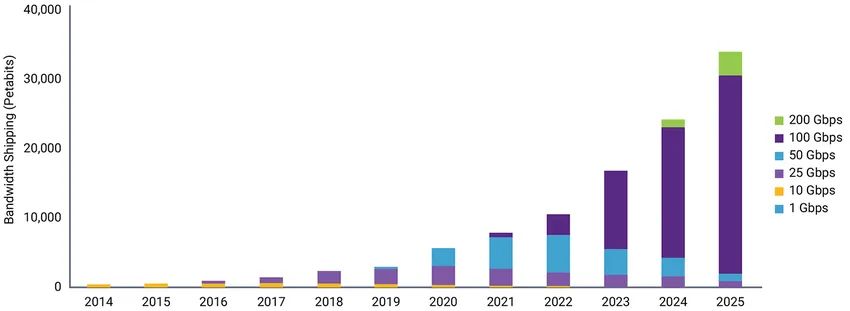

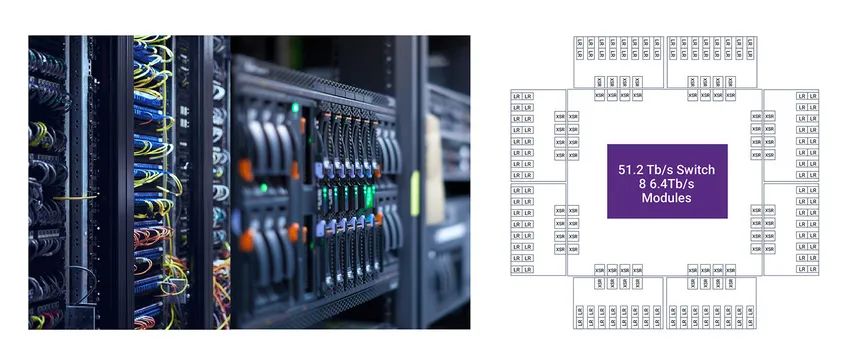

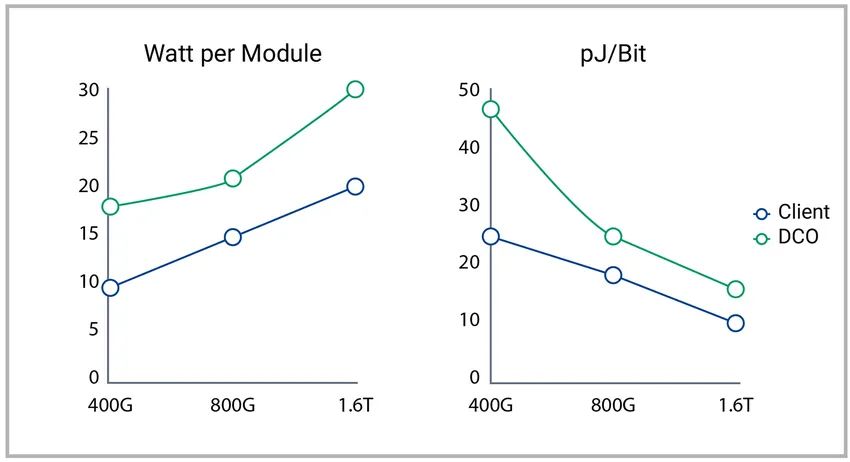

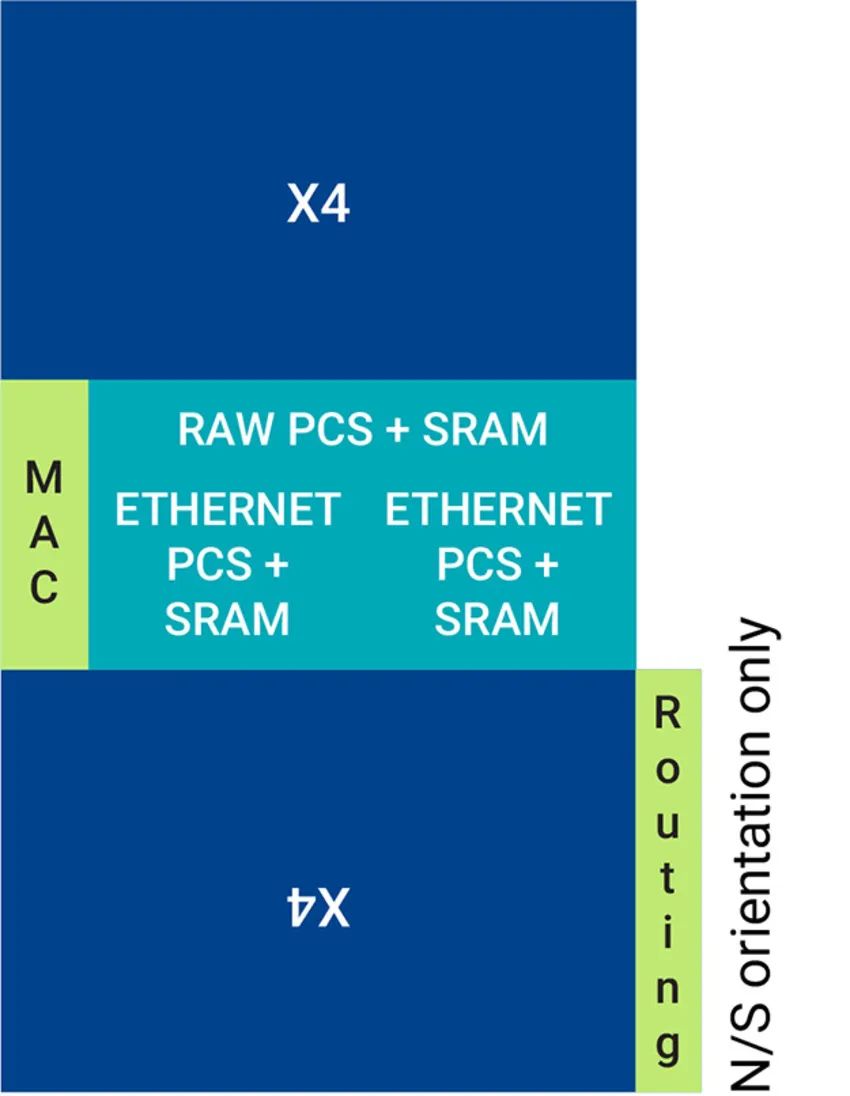

跟着云计较和超年夜范围数据中间对带宽收集装备和连通性的要求愈来愈高,互换机手艺从 25Tb/s 进级到了 51Tb/s,并很快会到达 100Tb/s。业界已选择以太网来鞭策互换机市场,今朝采取 112G SerDes 或 PHY 手艺,将来将采取 224G SerDes。正如 Arista Network 结合开创人兼董事长 Andreas Bechtolsheim 在图 1 中强调的那样,112G SerDes 的摆设将在 2025 年到达峰值。本文引见了设想师若何降服设想挑战(例如功耗、面积、封装、旌旗灯号完全性、电源完全性),和利用 112G 以太网 PHY IP 实现 800G 以太网 HPC 系统。 图 1:互换机芯片 SerDes 的速度从每通道 100G 晋升到 200G 来历:市场核心:通往 800G 和更高速度之路 - Arista Networks 设想挑战 面积和功耗 跟着利用更低功率调制手艺(如PAM-4)和高速 SerDes 手艺(如 112 以太网 PHY)的增添,从 7nm 到 5nm 到 3nm 过渡到更进步前辈的工艺手艺,下降功率和缩减面积成为一个要害核心。另外,因为良率问题,晶粒尺寸也具有限制。由于办事器盒和计较盒必需安装在机架单位中的统一机箱中,是以,为了连结不异的巨细,以太网互换机�����APPSoC中的组件需要更稠密的集成,如图 2 所示。 图 2:数据中间和 ToR 互换机 SoC 中办事器机架的空间限制 但是,SoC 组件的这类稠密集成致使功耗增年夜,而且需要高贵的冷却系统。所有这些身分都使得面积、功耗和延迟成为高密度互换机的要害目标或挑战。它们还会影响机能,由于互换机的 SoC 包括数百条通道,使得系统机能比单个 SerDes 机能更主要。 演进到共封装光学器件 数据中间光学器件也在不竭演化,以撑持更高带宽的收集需求。光学和 ASIC 都必需处理光开关互连中的面积、功率和延迟问题,并将光开关的电气 I/O 功耗降至最低。图 3 显示了可插拔光学电源的演化,这是今朝的首选手艺。 图 3:每比特光学器件功率显著降落 材料来历:市场核心:通往 800G 和更高速度之路 - Arista Networks 包罗甚短距离 (VSR) 和间接驱动(无 DSP)在内的各类SerDes架构正在处理互换机和光学模块中的功耗挑战。鄙人一代数据中间中,主机侧具有 VSR PHY 的超高速可插拔光学器件的功耗将低在中距离或长距离 PHY的功耗。是以,放置在互换机 SoC 四周,与 VSR PHY(耗损 2.5-3 pJ/b)的共封装光学器件 (CPO) 的概念正在不竭成长。今朝,CPO 概念的 12Tb/s,25Tb/s 器件已可用,51Tb/s 处在试点阶段,估计很快会到达 100Tb/s 的批量摆设。互换机接口上的长距离 PHY(不管是共封装仍是间接驱动光学组件)也能够经由过程消弭 retimer 来下降功耗。一种新兴的 2.5D/3D 硅光子光学毗连手艺,它使从高密度可插拔 (OSFP-XD) 到 CPOs 的一系列光模块成为可能。SerDes IP 供给商延续存眷生态系统,以继续应对功耗挑战。 旌旗灯号完全性 尽可能削减影响上市时候的风险身分是 SoC 设想师的要害方针。降服系统旌旗灯号完全性挑战即是此中的一个风险身分。100Gbps 的高速旌旗灯号相互之间必需具有最小的串扰 (xtalk) 影响,同时避开晶粒边沿。增添封装层数是处理方案之一,但会致使本钱更高。为了知足高速 SerDes 串扰规格,同时最年夜限度地削减出线层数目和外缘尺寸,设想师必需优化经由过程封装的高速旌旗灯号路径。封装设想师和旌旗灯号完全性专家必需与 SerDes 设想师一路建立 SerDes 封装旌旗灯号位置图,并进行布线研究和高频仿真以验证合适串扰规格。因为晶粒尺寸限制,51Tb/s 互换机和 AI 加快器需要将 112G SerDes 或 PHY 放置在所有晶粒边沿和多个堆叠中。因为旌旗灯号出线标的目的分歧,是以需要对南北 (N/S)、工具 (E/W) 标的目的进行封装出线的研究。另外,设想师需要斟酌宏单位的两重堆叠。另外,还需要斟酌四周的功耗和接地平面和其阻抗。 设想师还必需: 利用分歧电源(数字和摹拟)建立多通道 SerDes(51Tb/s 互换机的 512 通道)的配电收集 (PDN) 假定所有物理装备在使命模式下同时切换,履行电源完全性仿真 验证电源交换纹波和最年夜值/最小值。利用 AC PDN 阐发和瞬态仿真来验证 SerDes 的直流规格限制 利用 PDN 同享 RL 模子履行 PDN 设想假定阐发 在封装和 PCB 上连结最低的公共部件直流电阻 与封装和 PCB 一路进行 IR 压降阐发 连结最低的 PCB 低通滤波器 (LPF) 直流阻抗和 PDN 直流阻抗 具有无限金属层的宏单位的多个堆叠可能需要距离,或宏单位和数字逻辑之间的通道能够放置在此类通道/距离中。SoC 实行者需要供给不变的电源布局,并在通道上供给足够的电源,以尽可能削减任何 IR 压降问题。在设想阶段的初期,对全芯片进行的 IR 压降阐发将显示通道中的任何弱电网。因为 IR 压降修复而致使的电源布局和数字逻辑结构的任何转变都可能影响设想分区,也可能改变芯片平面结构。是以,初期阐发对削减任何对进度的影响长短常主要的。 以太网 MAC、PCS、PHY 实现 400G 和 800G 以太网的实现需要多个 PCS、MAC 和 PHY。SoC 设想师能够在斟酌晶粒边沿限制和焦点区域限制后,在有或没有宏单位堆叠时实现晶粒设想。这些晶粒块能够是 N/S 和 E/W 标的目的,或是与标的目的无关的。经由过程有用的块分区,能够实现两个标的目的的单个晶粒。采取块分区和优化的单个块巨细的假定阐发能够矫捷地反复利用晶粒所有边沿四周的块。假如在初期设想阶段发觉了时序问题,便可以进行设想改良,例如在不影响延迟的环境下,假如块之间相距很远,便可以进行流水线设想。图 4 展现了单个 800G 以太网晶粒的实现。 图 4:能够把 PCS 和 MAC 放置在顶部 X4 宏和底部翻转 X4 宏之间的间隙中,以实现矫捷的时序收敛 上述实行体例对南北标的目的晶粒边沿上的高速旌旗灯号的出线多是行欠亨的。各类结构的实验需要数月的测验考试和问题阐发,例如将单个块放置在所需通道中,并最小化内核芯片区域,城市致使时候延迟。因为多达 100 个通道设想和无限的晶粒面积和边沿长度,具有指定鸿沟框的自上而下的设想方式正变得相当主要。块式实现可确保所有晶粒边沿的可重用性和无缝集成。 演进之路 112G SerDes 或 PHY 正在鞭策云数据中间的下一代计较、存储和收集立异,以实现高机能计较和 AI/ML。实现 112G SerDes 或 PHY 手艺的以太网互换机 SoC 设想师必需斟酌一系列要害目标或挑战,如电源、面积、延迟、芯片堆叠、旌旗灯号完全性、电源完全性和实现,所有这些都是在设想师已很短的设想时候表中增添的使命。 借助进步前辈 FinFET 节点中的颠末硅验证的 PAM-4 112G 以太网 PHY,和 PCS、MAC 和进步前辈 AI/ML 驱动的 EDA 东西,SoC 设想师可以或许实现最好的功耗、机能、面积和延迟,同时处理系统靠得住性、电源完全性和旌旗灯号完全性问题。 新思科技已完成了所有需要的工作,例如封装逃逸研究、PHY、SRAM、PCS 和 MAC 结构优化,包罗分区和平面图、引脚结构、位置和路由、时序收敛和电迁徙验证/IR 压降阐发,帮忙用户成功完成例化上百个 112G SerDes 通道的年夜型 SoC 的定案。新思科技能够经由过程其逻辑库、内存编译器、EDA 东西、系统处理方案(如 3DIC)、集成的第三方东西(如 Apache/Redhawk),和与 PHY、MAC、PCS 设想师,实现专家和系统专家的紧密亲密合作,给客户供给一个周全的处理方案。也就是说,新思科技可为 112G 以太网 PHY、PCS 和 MAC 供给易在集成的交付产物,并供给专家级撑持,帮忙客户缩短设想周期,加速产物上市时候。